## **Ladder Diagrams**

Ladder Diagrams Logic gates Truth tables

1. Output bit 0 in IO Simulator matches Q5 in PLC. (1 point)

False

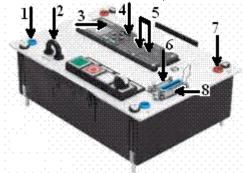

2. Match The LOGO! EduTrainer components and names: (16 points)

- a. 24 VDC socket

- b. Two expansion modules

- c. EMERGENCY-STOP bridge

- d. 0 VDC socket

- e. Submin-D socket

- f. SysLink interface

- g. LOGO! Basic

- h. Interface unit

| 3. | For OFF Delay timer the output isuntil |

|----|----------------------------------------|

|    | a defined time has expired. (1 point)  |

- 4. For LOGO PLC one of the following sockets is used for analogue signal: (2 points)

- Interface socket

- Submin-D socket

- SysLink socket

- 24 VDC socket

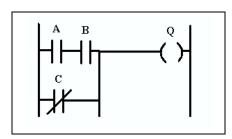

- 5. The following diagram is called: (2 points)

- Circuit diagram

- Logic gates diagarm

- Cadder diagram

- Function Block Diagram

| 6. |         | An input pulse increments or decrements ernal value, depending on the parameter setting (1 point) |  |  |  |  |

|----|---------|---------------------------------------------------------------------------------------------------|--|--|--|--|

| 7. | Which   | Which one of the following is NOT contact (Break Contact): (2 points)                             |  |  |  |  |

|    | 0       |                                                                                                   |  |  |  |  |

|    | 0       | (\)                                                                                               |  |  |  |  |

|    | 0       | \                                                                                                 |  |  |  |  |

|    | 0       | ( )                                                                                               |  |  |  |  |

| 8. | To ins  | ert a time delay relay SF must be selected. (1 point)                                             |  |  |  |  |

|    | 0       | True                                                                                              |  |  |  |  |

|    | $\circ$ | False                                                                                             |  |  |  |  |

| 9. | For Of  | N dealy timer The output is until a configured delay time has expired. (1 point)                  |  |  |  |  |

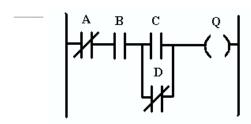

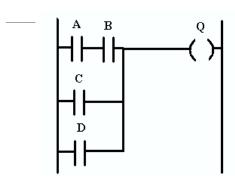

b.

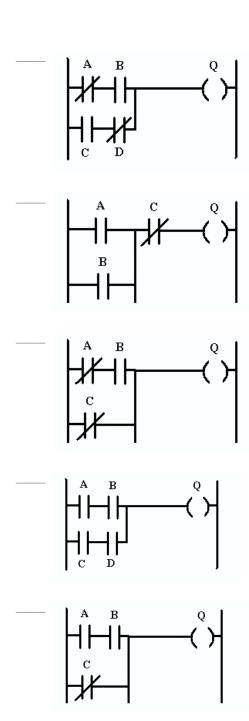

$$(\overline{A}.B).(C \cdot \overline{D})$$

d.

$$(\overline{A}.B)+(C\cdot\overline{D})$$

g.

$$(\overline{A}.B).(C+\overline{D})$$

h. (A+B).

$$\overline{C}$$

(A.B)+

$$\overline{C}$$

j.

$$A.B.\overline{C}$$

11. The given truth table represnts : (2 points)

| A | В | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 0      |

| 1 | 0 | 0      |

|   | 1 |        |

|     | 0              | AND gate                                                           |  |  |  |

|-----|----------------|--------------------------------------------------------------------|--|--|--|

|     | 0              | OR gate                                                            |  |  |  |

|     | 0              | NAND gate                                                          |  |  |  |

|     | 0              | NOT gate                                                           |  |  |  |

| 12. | Hours<br>(1 pc | Counter may widely be used for schedulingint)                      |  |  |  |

| 13. | The co         | ontroller which is able to work in sever conditions is: (2 points) |  |  |  |

|     | 0              | Computer                                                           |  |  |  |

|     | 0              | PLC                                                                |  |  |  |

|     | 0              | Microcontroller                                                    |  |  |  |

|     | 0              | Microprocessor                                                     |  |  |  |

| 14. | The re         | ason(s) why we need Hardware Controller is (are): (2 points)       |  |  |  |

|     | 0              | To reduce time                                                     |  |  |  |

|     | 0              | To increase the quality                                            |  |  |  |

|     | 0              | To allow for change                                                |  |  |  |

|     |                |                                                                    |  |  |  |

All answers are correct

## **Ladder Diagrams**

Ladder Diagrams Logic gates Truth tables

- 1. True

- 2. d, c, g, h, b, e, f, a

- 3. not reset, ON

- 4. Submin-D socket

- 5. Ladder diagram

- 6. Up/Down Counter, up down counter, counter

- 7. --|\|--

- 8. True

- 9. not switched on, off

- 10. b, f, g, a, j, d, h, c, e, i

- 11. AND gate

- 12. maintenance

- 13. PLC

- 14. All answers are correct